# LAP Installation Guide

LAP-321000U-A / LAP-322000U-A LAP-16128U / LAP-32128U-A

The Zeroplus Logic Analyzer Installation Guide

## Index

| Pr | eface                                                | . 2 |

|----|------------------------------------------------------|-----|

| 1  | Features of the Zeroplus Logic Analyzer              | . 3 |

|    | 1.1 Package Contents                                 | 3   |

|    | 1.2 Introduction                                     | 5   |

|    | 1.3 Hardware Specifications                          | 8   |

|    | 1.4 System Requirements                              | 9   |

|    | 1.4.1 Operating System Requirements                  | 9   |

|    | 1.4.2 Hardware System Requirements                   | 9   |

|    | 1.5 Device Maintenance and Safety                    | 10  |

| 2  | Installation                                         | 12  |

|    | 2.1 Software Installation                            | 12  |

|    | 2.2 Hardware Installation                            | 14  |

|    | 2.3 Tips and Advice                                  | 16  |

|    | 2.4 Flow of software operation                       | 18  |

| 3  | Introduction to Logic Analysis                       | 19  |

|    | 3.1 Logic Analysis                                   | 19  |

|    | Task 1. Clock Source (Frequency) and RAM Size set up | 19  |

|    | Task 2. Trigger Properties Setup                     | 21  |

|    | Task 3. Signal/Bus Trigger Edge Setup                |     |

|    | Task 4. Run to Acquire Data                          |     |

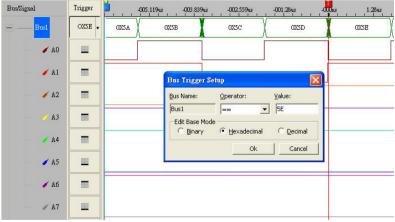

|    | 3.2 Bus Logic Analysis                               |     |

# Preface

This Quick Start Guide is designed to help new and intermediate users navigate and perform common tasks with the Zeroplus Logic Analyzer. Despite its simple packaging and interface, the Logic Analyzer is a sophisticated measurement and analysis tool. It is also a highly sensitive electrical current sensing device. Users must carefully read instructions and procedures pertaining to installation and operation. Any instrument connected to the unit should be properly grounded. A pair of anti-static gloves is strongly recommended when performing a task with the device. To ensure accuracy and consistency of output data, use of the bundled components is strongly recommended.

User opinions are very important to Zeroplus. Please contact our engineering team by telephone, fax or email with your questions or feedback. Thank you for choosing the Zeroplus Logic Analyzer.

### **1** Features of the Zeroplus Logic Analyzer

In this chapter, users will learn about the package contents, description, hardware specifications, system requirements, and safety issues of the Zeroplus Logic Analyzer. Though this chapter is purely informative, we highly recommend reading this carefully to ensure safety and accuracy when performing any operation with the Zeroplus Logic Analyzer. Analyzer.

### **1.1 Package Contents**

Verify the package contents before discarding packing materials. The following components should be included with your product. For assistance, please contact our nearest distributor.

| Models                        | LAP-16128U | LAP-32128U-A | LAP-321000U-A | LAP-322000U-A |

|-------------------------------|------------|--------------|---------------|---------------|

| Logic Analyzer                | 1          | 1            | 1             | 1             |

| 16-Pin Testing<br>Cable       | 0          | 1            | 1             | 1             |

| -Pin Testing Cable            | 2          | 2            | 2             | 2             |

| Probe                         | 20         | 36           | 36            | 36            |

| USB Cable                     | 1          | 1            | 1             | 1             |

| Getting Started<br>Guide      | 1          | 1            | 1             | 1             |

| Driver CD**                   | 1          | 1            | 1             | 1             |

| -PinTesting Cable<br>(White)  | 1          | 1            | 1             | 1             |

| -Pin Testing Cable<br>(Black) | 1          | 1            | 1             | 1             |

Table 1-1: Parts list for retail packages

\* This Driver CD consists of a multilingual software interface program, as well as a multilingual User's Manual.

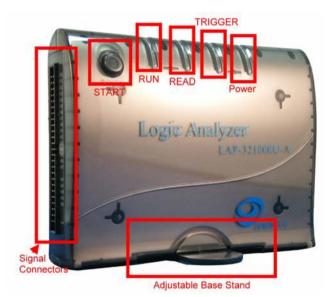

Fig. 1-1: Logic Analyzer

Fig. 1-3: Probes (varied depending on models)

Fig. 1-5: Getting Started Guide

Fig. 1-7: 1-Pin External Clock Wire (White)

16-Pin x 1 8-Pin x 2

Fig. 1-2: Testing Cables

Fig. 1-4: USB Cable

Fig. 1-6: Driver CD

Fig. 1-8: 2-Pin Ground Wire (Black)

### 1.2 Introduction

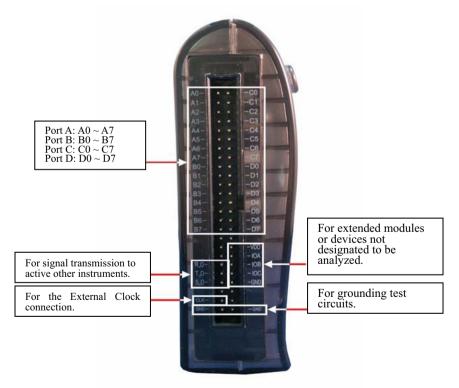

Zeroplus Logic Analyzer models LAP-16128U, LAP-32128U-A LAP-321000U-A and LAP-322000U-A all share the same external features as illustrated in the following figures.

Fig. 1-9: A view of the Zeroplus Logic Analyzer LAP-A Series. see *Fig 1-12* for detailed information on the **Signal Connectors**.

Fig. 1-10: Side view of the Zeroplus Logic Analyzer, which draws its power from the USB connection.

- Fig. 1-11: The above illustration demonstrates how the Base Stand Support may be adjusted. Gently pull the plate away from the analyzer, rotate it 90° and release it.

- Fig. 1-12: Rear view of the Zeroplus Logic Analyzer LAP-A Series.

| Models                  | LAP-16128U | LAP-32128U-A | LAP-321000U-A | LAP-322000U- |

|-------------------------|------------|--------------|---------------|--------------|

| 'ort A ( <b>A0~A7</b> ) | Х          | Х            | Х             | Х            |

| 'ort B ( <b>B0~B7</b> ) | Х          | Х            | Х             | Х            |

| 'ort C ( <b>C0~B7</b> ) |            | Х            | Х             | Х            |

| 'ort D ( <b>D0~B7</b> ) |            | Х            | Х             | Х            |

| R_0                     | Х          | Х            | Х             | Х            |

| T_0                     | Х          | Х            | Х             | Х            |

| \$_0                    | Х          | Х            | Х             | Х            |

| CLK                     | Х          | Х            | Х             | Х            |

| GND                     | Х          | Х            | Х             | Х            |

| VDD                     | Х          | Х            | Х             | Х            |

| IOA                     | Х          | Х            | Х             | Х            |

| IOB                     | Х          | Х            | Х             | Х            |

| IOC                     | Х          | Х            | Х             | Х            |

| GND                     | Х          | Х            | Х             | Х            |

#### : List of functional pins in each model.

#### Table 1-2: Definitions and Functions of pins for all models.

| CLK | Clock  | Connects a given external module to be analyzed.      |  |  |

|-----|--------|-------------------------------------------------------|--|--|

| GND | Ground | Two pins used for grounding the Logic Analyzer with a |  |  |

| _   |        | given external module to be analyzed.                 |  |  |

### Table 1-3: Definitions and Functions of pins for advanced models (1).

| R_O | Read (Out)    | When the Logic Analyzer is about to upload data from<br>memory to the PC, the <b>R_O</b> will send a <b>Rising Edge</b><br>signal of DC3.3V. When the upload is finished, a<br><b>Falling Edge</b> signal is sent.                                                  |  |  |

|-----|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| т_о | Trigger (Out) | When a trigger condition is established, the <b>T_O</b> will<br>send a <b>Rising Edge</b> signal of DC3.3V. When memory<br>is full, a <b>Falling Edge</b> signal is sent.                                                                                           |  |  |

| s_0 | Start (Out)   | When a user initiates a sampling task by clicking the RUN icon in the window or clicking the START button on the device, the <b>R_O</b> will send a <b>Rising Edge</b> signal of DC3.3V. When the Logic Analyzer finishes uploading, a falling edge signal is sent. |  |  |

Table 1-4: Definitions and Functions of pins for advance models (2).

| VDD | Voltage Drain     | Provides +3.3 V for external modules by draining   |

|-----|-------------------|----------------------------------------------------|

| VDD | (Semiconductor)   | voltage from the Logic Analyzer.                   |

| ΙΟΑ | Ext. I/O Module A | Transmits signals from an external model or device |

| IUA | EXI. I/O WOULLE A | not being tested.                                  |

| IOB | Ext. I/O Module B | Same as <b>IOA</b> .                               |

| IOC | Ext. I/O Module C | Same as <b>IOA</b> .                               |

| GND | Ground            | Grounds external devices, in sequence              |

### **1.3 Hardware Specifications**

### Table 1-5: Hardware specifications of LAP-A Model.

| Items\Type                            | LAP-16128                               | LAP-32 | 128U-A   | LAP-321000U-A  | A LAP-322000U |

|---------------------------------------|-----------------------------------------|--------|----------|----------------|---------------|

| Interface                             | USB 2.0 (1.1)                           |        |          |                |               |

| <b>Operating System</b>               |                                         |        |          |                |               |

| Power Supply                          |                                         | USB 1. | 1 (USB 2 | 2.0 Recommende | ed)           |

| Channels                              | 16                                      |        |          | 32             |               |

| Bandwidth                             |                                         |        | 75       | 5MHz           |               |

| Memory                                |                                         |        | 4N       | /I Bits        |               |

| Memory Depth<br>(Per Channel)         | 128 Kbits 128 KBits 1 MBits 2           |        |          |                | 2 MBits       |

| Internal Clock Rate<br>(asynchronous) | 100 ~ 200 MHz                           |        |          |                |               |

| Max External Clock<br>(synchronous)   | ۲ Max 100MHz                            |        |          |                |               |

| Trigger Channels                      | 16 Channels 32 Channels                 |        |          | els            |               |

| Trigger Condition                     |                                         |        | Edge     | /Pattern       |               |

| Pre-Trigger/<br>Post-Trigger          |                                         |        | Ň        | Yes            |               |

| Trigger Level                         |                                         |        | 11       | Level          |               |

| Trigger Count                         |                                         |        | 1-6      | 65535          |               |

| Max Trigger Page                      |                                         |        | Max      | x 8191         |               |

| Enable Channel                        | 16 32                                   |        |          |                |               |

| Buses Data                            | Yes                                     |        |          |                |               |

| Enable Delay                          | Start: Edge and Pattern<br>End: 1-65535 |        |          |                |               |

| Compression                           | 16 Cha<br>Compressio                    |        | 24       | Channel Compre | ession 1-255  |

### **1.4 System Requirements**

This section discusses basic operating system and hardware requirements for the Logic Analyzer. Software and hardware capabilities may vary depending on PC configuration,. This manual assumes proper installation of a supported operating system as listed below.

### 1.4.1 Operating System Requirements

In this sub-section, we share our experiences testing the Zeroplus Logic Analyzer on the following Microsoft Windows operating systems. Since the Zeroplus Logic Analyzer requires operating system support of the USB protocol, Windows 95r2 and earlier OS versions are incompatible.

- 1) Windows 98, 98 Second Edition supported

- 2) Windows ME -- supported

- 3) Windows 2000 Professional, Server Family supported

- 4) Windows XP Home, Professional Editions (32-Bit versions) supported

### 1.4.2 Hardware System Requirements

• CPU

Windows NT, 98, 98 SE 166 MHz, or above. Windows 2000, XP 300 MHz, or above (strongly suggest 900 MHz, or above).

We have tested various 32-Bit and 64-Bit CPUs. Overall, we find that all 32-Bit CPUs work very well with Logic Analyzer software. Moreover, we find that AMD's 64-Bit CPUs, except Opteron, with a 64-Bit Windows operating system, work just fine with Logic Analyzer; no significant problems occur.

#### • Memory

Windows NT, 98, 98 SE 128 MB or above (64 MB minimum). Windows 2000, XP 256 MB or above (128 MB minimum).

### Hard Drive

At least 100 Mb available space.

USB

USB 1.1 compatible (recommend USB 2.0).

- Display Devices (recommended)

- 1. 17" monitor with 1024x786 resolution or higher.

- 2. 8MB SDRAM on Video Card.

### **1.5 Device Maintenance and Safety**

Follow these instructions for proper operation and storage of the Logic Analyzer.

| Cautions | <ul> <li>Do not place heavy objects on the Zeroplus Logic Analyzer.</li> <li>Avoid hard impacts and rough handling.</li> <li>Protect the Logic Analyzer from static discharge.</li> <li>Do not disassemble the Zeroplus Logic Analyzer; this will void the warranty and could affect its operation.</li> </ul> |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cleaning | <ul> <li>Use a soft, damp cloth with a mild detergent to clean.</li> <li>Do not immerse or spray any liquid on the Zeroplus Logic<br/>Analyzer</li> <li>Do not use harsh chemicals or cleaners containing substances<br/>such as benzene, toluene, xylene or acetone.</li> </ul>                               |

### Table 1-7: General Advice

#### **Table 1-8: Electrical Specifications**

| Items                      | Minimum  | Typical    | Maximum   |

|----------------------------|----------|------------|-----------|

| Working Voltage            | DC 4.5 V | DC 5.0 V   | DC 5.5 V  |

| Current at Rest            |          |            | 200 mA    |

| Current at Work            |          |            | 400 mA    |

| Power at Rest              |          |            | 1 W       |

| Power at Work              |          |            | 2W        |

| Error in Phase Off*        |          |            | ± 1.5 ns  |

| Vinput of Testing Channels |          |            | ± DC 30 V |

| V <sub>Reference</sub>     | DC -6V   |            | DC +6 V   |

| Input Resistance           |          | 500KΩ/10pF |           |

| Working Temperature        | 5°C      |            | 70°C      |

| Storage Temperature        | -40°C    |            | 80°C      |

Table 1-9\* refer to the User Manual for error analysis calculation.

| WARNING                | <ul> <li>Avoid direct sunlight</li> <li>Use in a dust free, non-conductive environment (see Note)</li> <li>Relative Humidity: &lt; 80%</li> <li>Altitude: &lt; 2000m</li> <li>Temperature: 0 ~ 40 degrees C</li> </ul> This is a Class A product which may cause radio interference in a domestic environment. Note: EN 61010-1:2001 specify degrees of pollution and their requirements. Logic Analyzer falls under Level 2. Pollution refers to 'addition of foreign matter, solid, liquid or gaseous (ionized gases), that may produce a reduction of dielectric strength or surface resistivity'. Pollution Degree 1: No pollution or only dry, non-conductive pollution occurs. This pollution has no effect. Pollution Degree 2: Normally only non-conductive pollution |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Pollution Degree 2: Normally only non-conductive pollution occurs. Occasionally, however, temporary conductivity caused by condensation must be expected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                        | Pollution Degree 3: Conductive pollution occurs or dry,<br>non-conductive pollution occurs which becomes conductive due<br>to condensation. In such conditions, equipment is normally<br>protected against exposure to direct sunlight, precipitation and<br>wind, but neither temperature nor humidity is controlled.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Storage<br>Environment | Relative Humidity: < 80%<br>Temperature: 0 ~ 50 Degrees C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### : Operating Environment

### Conclusion

After reading this section, users should have a basic grasp of the Logic Analyzer. A complete understanding of the **Safety and Care Recommendations section** is a critical prerequisite of any further operation as presented in the User Manual.

### 2 Installation

This chapter describes installation of the Logic Analyzer hardware and software. Software installation steps must be followed precisely to ensure successful installation.

### 2.1 Software Installation

In this section, users will learn how to install the software interface and drivers. As with proper installation of many USB devices, the Logic Analyzer application and driver software must be installed prior to connection of the hardware. The following steps illustrate an installation of a Zeroplus **LAP-32128U-A** Logic Analyzer. The other two models mentioned in Chapter 1 would follow identical procedures.

- Step 1. Insert the driver CD-ROM in the PC CD drive.

- Step 2. Execute the installation program. Go to the START menu, click START, click Run, click Browse, select Setup.exe file in the appropriate model folder and then click OK. It is recommended that all other programs are closed while installation proceeds.

- Step 3. Choose the desired language.

- Step 4. Click Next to proceed with the Install wizard

- Step 5. Select "I accept the term in this license agreement, " and click Next.

- Step 6. Enter User and Organization name.

- Step 7. Choose the setup type. We recommend Complete for most users.

- Step 8. Click Install to confirm settings and begin actual installation.

- **Step 9.** Click **Yes** to acknowledge the Microsoft Digital Signature message and continue the installation.

- Step 10. Click Finish to complete the installation.

- Step 11. Click Yes to restart the PC.

The Zeroplus Logic Analyzer Installation Guide

### 2.2 Hardware Installation

Hardware installation simply involves connecting the Logic Analyzer to your computer with the included USB Cable as shown in Figures 2-4 and 2-5.

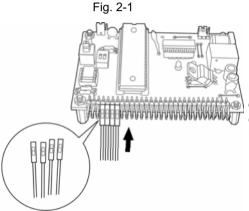

1. Plug the fixed end of the cables into the LA (Fig.2-1).

2. Plug the loose ends into the connectors on the circuit board to be analyzed (Fig.2-2).

**Note:** The following sequence must be observed when connecting the connectors into the circuit board: A0 = Brown, A1 = Red, A2=Orange and so on.

Fig. 2-2

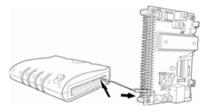

3. The circuit board must be grounded to the Logic Analyzer with the connecting cables (Fig.2-3).

Fig. 2-3

- Step 1 Plug the thin male end of the USB cable into the laptop or PC.

- Step 2 Plug the square female end into the logic analyzer.

Fig. 2-4

5. Plug the thin end into the computer (Fig.2-5).

4. Plug the square end of the USB cable into the Logic Analyzer (Fig.2-4).

Fig. 2-5

At this point, the computer should be able to detect the Logic Analyzer and finalize the installation for hardware connection. For further information, refer to the Troubleshooting and Frequently Asked Questions (FAQ) chapters in the User Manual.

Fig. 2-6: An assembly of Laptop, Logic Analyzer, and a testing board.

### 2.3 Tips and Advice

- 1. When testing a circuit board, make sure that the internal sampling frequency (within the Logic Analyzer) is at least four times the external board frequency.

- 2. If the signal connector does not work well with the pins on the test board, try using the supplied probes.

Fig. 2-7: Probes supplied with the Zeroplus.

- 3. Usages of probes

- 3-1. Take the loose end of the cable and insert it into the clip.

Fig. 2-9

- 3-2. Compress the probe as shown to reveal 2 metal prongs (Fig.2-8).

- 3-3. Place the metal prongs on a metal connector on the motherboard and release the fingers so that the prongs grip the metal connector (Fig.2-9).

- 4. The Logic Analyzer will connect to the Zeroplus server for software updates if an internet connection is available.

- 5. Unwanted signals can be filtered out using the **Enable** or **Enable Delay** functions.

- 6. When measuring for a long period, **Compression** makes memory more efficient.

- 7. Trigger condition depends on the test board. If triggering does not work well, try narrowing the trigger conditions and optimize them repeatedly.

- 8. If a test board has a lower frequency than Logic Analyzer, sample signals according to the external clock.

- 9. When clocking by an external clock, filter extra signals with the Enable function.

- 10. Unused channels may be removed from the **Bus/Signal** display using **Bus/Signal** (Menu) → Channel Setup.

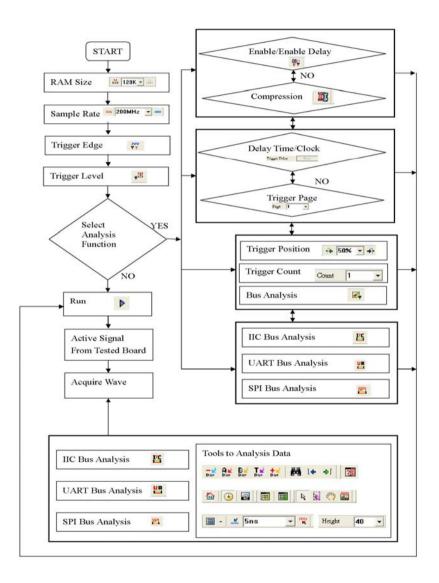

### 2.4 Flow of software operation

### **3** Introduction to Logic Analysis

Chapter 3 gives detailed instructions in performing two basic analysis operations and five advance analysis applications with the Logic Analyzer. The basic analytical operations are the Logic Analysis and the Bus Analysis, which are fundamental to all further applications.

### 3.1 Logic Analysis

Logic Analysis is meant for a single signal analysis. Section 3.1 gives detailed instructions on the software's basic setup.

Basic Software setup of the Logic Analysis

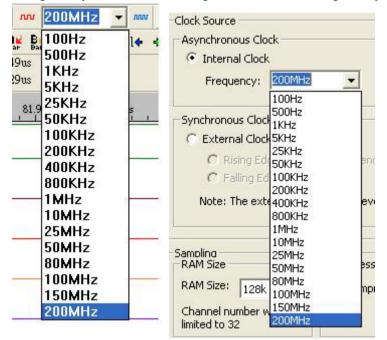

#### Task 1. Clock Source (Frequency) and RAM Size set up

**Step 1.** Click icon or Click Sampling Setup from Bus/Signal on the menu bar, the dialogue as shown in Fig 3-1 will appear.

| 🚳 ZER(             | OPLUS Logic Analyzer - []                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | laDoc1]                                                                                                                 |   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---|

| 🐔 <u>F</u> ile     | Bus/Signal Trigger Run/St                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | op <u>D</u> ata <u>T</u> ools <u>W</u> indow <u>H</u> elp                                                               |   |

| 🗋 🖻                | Second and a second sec | 🕴 📲 🌉 🕨 🕪 🔳 📲 128K 🕶 🗟                                                                                                  |   |

|                    | 🚜 Channels Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Sampling Setup                                                                                                          | 2 |

| Scale:1<br>Total:6 | Group into Bus Ctrl<br>Ungroup from Bus Ctrl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Clock Source                                                                                                            |   |

| Bus/Sig            | Expand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Internal Clock                                                                                                          |   |

| 8                  | Collapse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Frequency: 200MHz                                                                                                       |   |

|                    | Format Row<br>Rename                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Synchronous Clock                                                                                                       |   |

|                    | 🖌 🖌 🕅                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C Rising Edge Frequency: 100KH2<br>C Falling Edge (Min:0.001Hz, Max:100MHz)                                             |   |

|                    | 🖌 🖌 📈                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Note: The external clock voltage level is the same as the port trigger level                                            |   |

|                    | A3 .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Samolina<br>RAM Size<br>RAM Size: 128k  Compression Mode<br>Data compression<br>Channel number will be<br>limited to 32 |   |

|                    | a<br>Ja                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Apply OK Cancel Help Restore Defaults                                                                                   |   |

Fig 3-1 – Clock Source

Step 2. Internal Clock (Asynchronous Clock)

Click on Internal Clock, and then select the Frequency from the pull down menu to set up the frequency of the device under test (DUT). The frequency of the Internal Clock must be at least four times higher then the frequency of the Oscillator on the DUT. Or, select the frequency *complex complex compl*

**Tip:** Connect the signal output pin of the tested board to the Signal connector of Logic Analyzer to measure it using the internal clock of Logic Analyzer.

External Clock (Synchronous Clock)

Click on External Clock, and then select "Rising Edge" or "Falling Edge" as the trigger condition of the DUT. In the Frequency column, type the frequency of the oscillator on the DUT.

**Tip:** The External Clock is applied when the frequency of the oscillator on the tested board is less then 100MHz. Connect the output pin of oscillator on the tested board to the CLK pin of Logic Analyzer as shown in Fig 3-3.

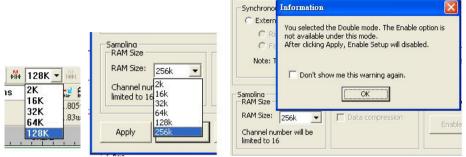

#### Step 3. RAM size

Click on the RAM size  $\boxed{2K}$   $\boxed{2K}$  from the pull down menu on the Sampling Setup dialogue as shown in Fig 3-3.

Fig 3-3 – RAM Size

**Tip:** The relationship between RAM size, Enable, Compression and channels as shown in Table 3-1 and Fig 3-3.

Table 3-1 RAM size vs Enable, and RAM size vs Compression and channels

| Model No.     | RAM<br>sizes/<br>channel | Channels<br>available | Compression<br>Mode &<br>Enable Mode | RAM<br>size/<br>channel | Channels<br>available | Compression<br>Mode &<br>Enable Mode |

|---------------|--------------------------|-----------------------|--------------------------------------|-------------------------|-----------------------|--------------------------------------|

| LAP-16128U    | 2K ~ 128K                | 16 channels           | Available                            | 256K                    | 16 channels           | Disable                              |

| LAP-32128U-A  | 2K ~ 128K                | 32 channels           | Available                            | 256K                    | 16 channels           | Disable                              |

| LAP-321000U-A | 2K ~ 1M                  | 32 channels           | Available                            | 2M                      | 16 channels           | Disable                              |

| LAP-322000U-A | 2K ~ 2M                  | 32 channels           | Available                            | 4M                      | 16 channels           | Disable                              |

### Task 2. Trigger Properties Setup

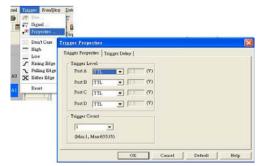

Step 1. Click icon or Click Properties from the Trigger on the Menu Bar. The dialogue will appear as shown in Fig 3-4.

The Zeroplus Logic Analyzer Installation Guide

### Fig 3-4 – Trigger Properties

Step 2. Trigger Level Setup

Click the drop down menu of Trigger Level on Ports A, B, C and D to select the Trigger Level as the voltage level that a trigger source signal must reach before the trigger circuit initiates a sweep.

**Tip:** There are four commonly used preset voltages for Trigger Level, TTL, CMOS (5V), CMOS (3.3V), and ECL. Users also may define their own voltage from -6V to +6V to fit with their DUT.

Port A represents the pins from A0 ~ A7 on the signal connector of the Logic Analyzer, and so do Ports B, C and D. The voltage of each port may be configured independently.

| frigger Properties 🛛 🔀                                        |

|---------------------------------------------------------------|

| Trigger Properties Trigger Delay                              |

| Trigger Level                                                 |

| Port A TTL V                                                  |

| Port B CMOS(5v) 2.5 (V)                                       |

| Port C CMOS(3.3) [1.65 (V)                                    |

| Port D ECL  Fils, (V)                                         |

| Trigger Co CMOS(5v) CMOS(3.3)                                 |

| ECL<br>User Define Flease enter a number between -6.0 and 6.0 |

| (Min:1, Max:65535) 確定                                         |

| OK Cancel Default Help                                        |

Fig 3-5 – Trigger Properties Error

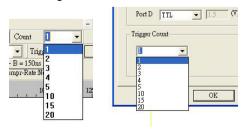

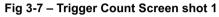

Step 3. Trigger Count.

Type the numbers or select the number from the pull down menu of the Count Count on the Tool Bar or Click the pull down menu of the Trigger Count on the Trigger Properties dialogue as shown in Fig 3-5

The system will be triggered where the Trigger Count is set as shown in Figs 3-6,3-7 and Fig 3-8.

| 📕 File Bys/Signal 🕻             | frigger Run/Sto | op <u>D</u> ata <u>I</u> ools <u>W</u> indow <u>H</u> e | lp                                 |               |                                    |                |                                |

|---------------------------------|-----------------|---------------------------------------------------------|------------------------------------|---------------|------------------------------------|----------------|--------------------------------|

| 🗅 😂 🖪 🎒                         | 🗛 🏹 🖗           |                                                         | I ₩4 128K - ₩ ₩ л                  | n 200MHz 💌    | ····· 10% -                        | → Page 1       | Count     1                    |

| 🗟 🔕 📾                           |                 | 🖑 🛗 📓 - 🧩 2.29                                          | 3us 👻 🙀 🙀 🗛                        | Bar Te te Bar | 🔹 🍕 🔯 🔡                            | 🞦 Height       | 40 • Trigger Delay             |

| Scale 2.293us<br>Total:655.36us | 10              | Display Pos:-013.571 us<br>Trigger Pos:Ons              | A Pos:-060.49us<br>B Pos:-060.34us |               | A - T = 60.49us<br>B - T = 60.34us | <b>•</b><br> • | A - B = 150ns<br>Compr-Rate:No |

| Bus/Signal                      | Trigger         | -0077,435 us -047.96                                    | 9ws -036.503ws -02                 | 25.087        | в -002105-в                        | 9.361us 2      | 0.827us 32.298us               |

| 🖌 🗚                             | <b>Z</b> -      |                                                         |                                    |               |                                    |                |                                |

| — 🖌 A1                          |                 |                                                         |                                    |               | Y                                  |                |                                |

|                                 |                 |                                                         |                                    |               |                                    |                |                                |

Fig 3-6 – Trigger Count Drop down Menu

| 😂 ZEROPLUS Logic                | Analyzer   | [LaDoc1]           |                           |                  |                   |                            |           |       |                                  |          |          | E                      |

|---------------------------------|------------|--------------------|---------------------------|------------------|-------------------|----------------------------|-----------|-------|----------------------------------|----------|----------|------------------------|

| 🕷 File Bus/Signal T             | rigger Run | ⊿Stop <u>D</u> ata | <u>T</u> ools <u>W</u> in | dow <u>H</u> elp |                   |                            |           |       |                                  |          |          |                        |

| 🗋 😂 🗟 💆                         | ų 🔍 🎋      |                    |                           | DD 🔳 👬           | 128K              | • 👸 nu                     | 200MHz    | z 💌 📶 | • 🐴 10%                          | 🔹 🐳 Page | 1 •      | Count 5                |

| 🐼 🐼 🐼                           | R          | N 🖑 🛅              | · ·                       | £ 2.293us        | - <sup>MU</sup> R |                            | F Bar Bar | M 14  | 🌒 🐻 💾                            | 💾 💾 Hei  | ght 40   | Trigger Delay          |

| Scale 2.293us<br>Total:655.36us |            | Display<br>Trigger |                           |                  |                   | ::-060.49us<br>::-060.34us |           |       | A - T = 60.49x<br>B - T = 60.34x |          |          | = 150ns +<br>r-Rate:No |

| Bus/Signal                      | Trigger    | ė, , , •           | 45.864us                  | -034.398us       | -022,982          | в <u>-011</u> .            | 166nis    | Uns . | 11.466us                         | 22.932us | 34.398us | 45.864us               |

| 🖌 🗚                             | <b>•</b>   |                    |                           |                  |                   | 1 2                        | 3 4       | 5     |                                  |          |          |                        |

| - 🖌 A1                          |            | -                  |                           |                  |                   |                            |           | Ш     |                                  |          |          |                        |

| 🥒 🥖 A2                          |            |                    |                           |                  |                   |                            |           |       |                                  |          |          |                        |

Fig 3-8 – Trigger Count Screen shot 2

Step 4. Trigger Page/ Delay Time and Clock

The Trigger Page and The Delay Time and Clock can't be applied at the same time.

### 1. Trigger Page:

Click Trigger Page, then Type the numbers or select the numbers from the pull down menu of the Page Page 1 on the Tool Bar or Click the pull down menu of the Trigger Page on the "Trigger Delay" page of the Trigger Properties dialogue as shown in Figs 3-9,3-10 and 3-11. The page numbers selected will be displayed on the screen.

**Tip:** The Trigger bar (T bar) will not be displayed when the set up of the Trigger page is more than 1

|                                         | Trigger Properties Trigger Deley                                                                                                                |                                                                                                                          |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| age <mark>1</mark><br>Heigh 1<br>2<br>3 | Cou Traper has<br>Traper has<br>B = : 114<br>15<br>15<br>15<br>15<br>15<br>16<br>17<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>18 | C Delay Tane and Clock Taigar Delay Tane Gai, San, Max83.881an) Taigar Delay Clock Taigar Delay Clock Gai, LMax16778191) |

| 4<br>5<br>10<br>15                      | T Pot = Our , Shut Pot = -005 11                                                                                                                | er pages are aslected, the trigger her disappears from                                                                   |

| Scale 65 52us<br>Total 2 621ms |            | Display Pos:1 049ms<br>Trigger Pos:0ns | A Pos:962.58us -<br>B Pos:1.245ms -                                                                                                                                           | A - T = 962.585us<br>B - T = 1.245ms                       | A - B = 282 555m<br>Compr-Rate No |

|--------------------------------|------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|

| Bu/Signal                      | Trigger    | 35170a 45.70a                          | 393.38ez 720.98ez                                                                                                                                                             | 1049mm 1376mm 1.704mm                                      | 2031ms 2357mm                     |

| - <mark>- 1</mark> .5          | <b>z</b> . |                                        |                                                                                                                                                                               |                                                            |                                   |

| ✓ ∆5                           | 12         | 7                                      | rigger Properties                                                                                                                                                             |                                                            | ×                                 |

| # A7                           | 191        |                                        | Trigger Properties Trigger Delay                                                                                                                                              |                                                            | 1                                 |

|                                | Start P    | os (Ds) = -262.12us                    | C Tagger Page<br>Tagger Page<br>1 w<br>(1 w)<br>(4m, 1, Mox (28))<br>Tagger Position<br>1 Post = 0om, 3bat Post = -362 12m, R<br>Net: When nore than one bigger page<br>were: | Cancel Default International Clock     Cancel Default Help | End Pos (Dp)<br>= 2.359ms         |

#### Fig 3-9 – Trigger Page

Fig 3-10 – Trigger Position

| Scale 65 52us<br>Total 2.621ms | Display Pos 3 67ms<br>Trigger Pos Ons | A Por 3 584ms +<br>B Por 3 867mt +                                                                                                                                 | A - T = 3.584ms<br>B - T = 3.067ms                                                                                                                                                                                  | :     | A - B = 28<br>Compr-R |            |

|--------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|------------|

| Bus/Signal Ingges              | 2687m                                 |                                                                                                                                                                    | 3.67ms 3.998ms                                                                                                                                                                                                      | 432es | 4.653mm               | A Stime    |

|                                | ·                                     |                                                                                                                                                                    |                                                                                                                                                                                                                     | 10.00 | (1+11+)               |            |

| ▲ A6                           | Trisser                               | roperties                                                                                                                                                          |                                                                                                                                                                                                                     | ×     | 1                     |            |

| - # A7 🔤                       | Trigger i                             | toperfies Trigger Delay                                                                                                                                            |                                                                                                                                                                                                                     |       |                       |            |

| Start                          | -Ta<br>Tro                            | Trigger Page<br>Trigger Page<br>2 V<br>Min 1, Mox 1200<br>ager Polition<br>002 T<br>= One , Start Poo = 2.359 nm , End<br>When more than one trigger page<br>tive. | C Delay Tane and Clock<br>Trigger Delay Tane<br>Otto 2016, Mac 2018, Mac 2018<br>Trigger Delay Clock<br>Trigger Delay Clock<br>Otto: 1,Mac 166592251)<br>Por = 4 S91ms<br>an soloted, the trigger bit disappears to | from  | End Pos (Dp)          | ) = 4.981m |

Fig 3-11 – Trigger Position and screen

### 2. Delay Time and Clock

Click the Delay Time and Clock, then type the numbers into the column of the Trigger Delay Time or type numbers into the Trigger Delay Clock at the "Trigger Delay" page of the Trigger Properties dialogue as 0 and Fig 0. Or type the numbers into the column of Trigger Delay Trigger Delay 5ns on the Tool Bar. The system will display the wave start.

**Tip:** The formula of Delay Time and Clock is "Trigger Delay Time = Trigger Delay Clock \* (1/ Frequency)".

**Step 5.** Type the percentages or select the percentages from the pull down menu of the solution on the Tool Bar or Click the pull down menu of the Trigger Position on the "Trigger Delay" page of the Trigger Properties dialogue as shown in Figs 3-12, 3-13, 3-14, and 3-15, The Trigger Position percentages selected will be displayed where counted from the right side of the screen of the system.

Fig 3-12 – Trigger Position Drop down menu

|           | Totager Roadling |         |            | 128K +   | - 200MH | z + = G | - 0% -    | + Part 1 | +)Ca                           | at []    | •  |

|-----------|------------------|---------|------------|----------|---------|---------|-----------|----------|--------------------------------|----------|----|

|           |                  |         | ± 13.759us |          |         | A-:     | T=3.04m   | Bright   | 40 •<br>A • B = 15<br>Compe Ro |          |    |

| walligned | Trigger 🛄        | 56.530w | 125.383w   | 194,1754 | 303.904 | 331 774 | 400,566ha | 405,500  | 536.250w                       | 605.9544 | -  |

| A 10      | Z •              |         |            |          |         |         |           |          |                                |          |    |

| # A1      | M                |         |            |          |         |         |           |          |                                |          |    |

| 1 1.2     | 35               |         |            |          |         |         |           |          |                                |          |    |

|           |                  |         |            |          | a page  |         |           |          |                                |          | ĩ. |

Fig 3-13 – Trigger Position 0%

Fig 3-14 – Trigger Position 10%

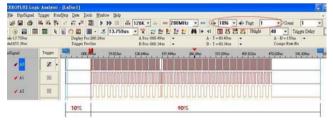

| Ble Bysfiguel              | Toger R | and top D | da Ioola H                   | indow Help |        |                  |          | <br>                 |          |                      |               |    |

|----------------------------|---------|-----------|------------------------------|------------|--------|------------------|----------|----------------------|----------|----------------------|---------------|----|

|                            |         |           |                              |            | 128K • |                  |          |                      |          | - 00                 | oest 1        | •  |

|                            |         |           |                              | ¥ 14.087us |        |                  | 2 M 1    |                      | E Bright |                      | Trigger Delay |    |

| nle:14.087m<br>obl:655.36m |         |           | play Fox-1243<br>ggrc FoxOan | (27 m)     |        | 705m •<br>555m • |          | 153.705m<br>153.555m |          | A - B = 1<br>Compr-R | SOm 💌<br>No   |    |

| largiller                  | Trigger |           | -406.664m                    | 336.229w   | -26.7% | -195.361w        | -124 927 | <br>Albur .          | 13900    | 863Zw                | 156.809w      |    |

| - <mark>- 1</mark> 10      | Z       | •         |                              |            |        |                  |          |                      |          |                      |               |    |

| × A1                       | - 30    |           |                              |            |        |                  |          |                      | nnnnnn   |                      |               |    |

| ▲ A2                       | 10      |           |                              |            |        |                  |          |                      | Innn     |                      |               |    |

|                            |         | 1         |                              |            | 70%    |                  |          |                      | 1        | 30%                  |               | ĩ. |

Fig 3-15 – Trigger Position 70%

Step 6. Click OK to confirm the setup and exit the Trigger Properties dialogue.

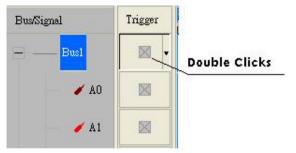

### Task 3. Signal/Bus Trigger Edge Setup

Highlight a designated signal, and then set its required trigger edge.

- 1. Left click to set the signal trigger edge as shown in Fig 3-16.

- 2. Right click \_\_\_\_\_ to set the signal trigger edge as shown in Fig 3-17.

- 3. Click Trigger on the menu bar and choose a trigger from the list of triggers as shown in Fig 3-18.

Fig 3-16 – Trigger Left click

Fig 3-17 – Trigger Right Click

Fig 3-18 – Trigger menu

#### Task 4. Run to Acquire Data

#### 1. Single Run

Click the Single Run i icon from the tool bar or press START button on top of Logic Analyzer (or press F5), then activate the signal from the DUT to the Logic Analyzer to acquire the data shown in the wave display area.

#### 2. Repetitive Run

Click the Repetitive Run  $\rightarrow$  icon from the tool bar, then activate continuous signal to the Logic Analyzer to acquire the repetitive Data, and then click the stop icon to end the repetitive run.

Tip: Click icon to view all the data, and then select the wave analysis tools to analyze the waves.

| ZEROPLUS Logic                   | Analyzer   | - [LaDoc1]                         |                                    |                                |        |           |                              |                                     |           |           |

|----------------------------------|------------|------------------------------------|------------------------------------|--------------------------------|--------|-----------|------------------------------|-------------------------------------|-----------|-----------|

| File B <u>u</u> s/Signal T       | rigger Rur | ⊿Stop <u>D</u> ata <u>T</u> ools   | <u>W</u> indow <u>H</u> elp        |                                |        |           |                              |                                     |           | - 8 ×     |

| ) 🧀 🖪 🍓 🏼                        | u, 🔍 🖗     | 🖓 🕂 📲 🔟                            | ▶ <b>▶</b> ■ <b>♦</b> ¶∢           | 128K 💌 🗰                       | 200MHz | z 💌 🛲 🦂 1 | 0% ▼ → Page                  | 1 • Count                           | 1         | •         |

| Cale:72.679KHz<br>Coale:655.36us | R          | Display Pos 250<br>Trigger Pos Ons | .932us                             | A Pos:-060.49<br>B Pos:-060.34 |        | A - T = 1 | 6.532KHz -<br>6.573KHz -     | 40  Trigge A - B = 6.667 Compr-Rate |           | 5ns       |

| us/Signal                        | Trigger    |                                    | 44.544125                          |                                |        | -         | 728us 388.524us              | 457.32us                            | 526.116us | 594.91: ^ |

| / A0                             | z          |                                    | tions of any option of an antional |                                |        |           | annana nanta nanta nanta nan |                                     |           |           |

| - × A1                           |            |                                    |                                    |                                |        |           |                              |                                     |           |           |

| <b>∕</b> A2                      |            |                                    |                                    |                                |        |           |                              |                                     |           | 3         |

| × A3                             |            |                                    |                                    |                                |        |           |                              |                                     |           | _         |

| A4                               |            |                                    |                                    |                                |        |           |                              |                                     |           |           |

| 🖌 A5                             |            |                                    |                                    |                                |        |           |                              |                                     |           |           |